# How to build an IC Company

Presentation to Stanford University EE380 – October 2020

## Do you have an idea worth pursuing?

Take measure of competitors

#### **GUIDANCE**

Talk to an advisor

#### **CUSTOMER**

Talk many possible customers

#### **INVESTOR**

Talk to a trusted investor in this space

Does a product exist that provides what you are proposing?

Talk to an advisor you trust who has experience in the industry you hope to enter

A possible customer will have important feedback on whether they would buy your product

Seek out feedback on likelihood of them or someone in their network investing in this product

August 2020 2000

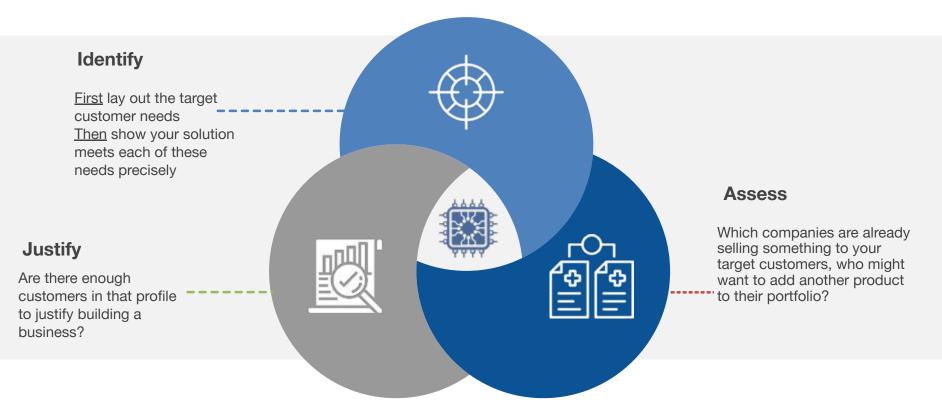

## Do You Have a product worthy of building a company?

August 2020 3@@

## What kind of company would you like to build?

Create a solutions companies that needs a new IC

August 2020 4@@

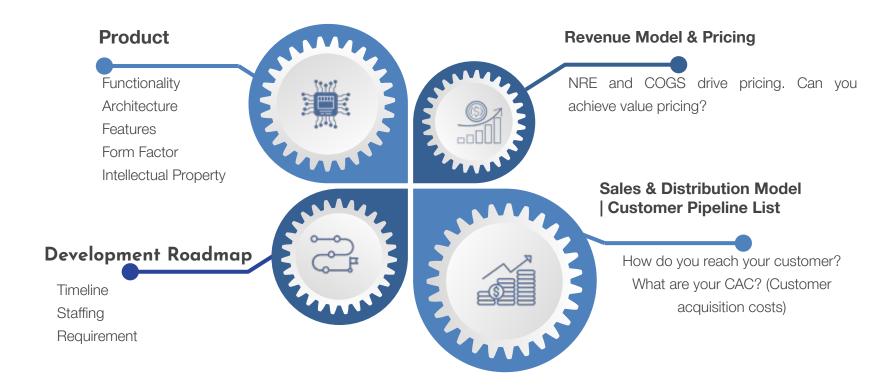

### **Business plan/Go To Market**

These items will drive your costs and how much money you need to raise.

August 2020 5000

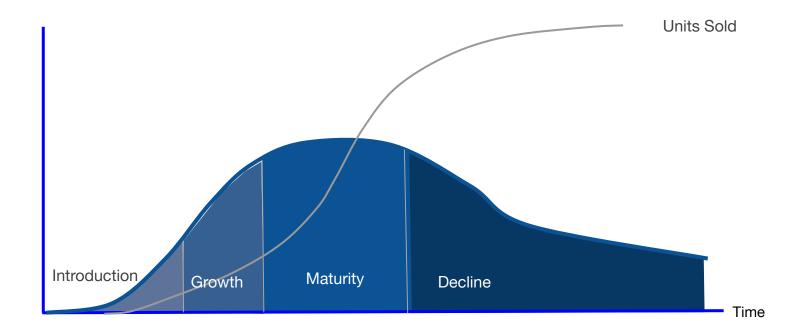

## Why now?

Will the market be ready?

Can your product be developed in time for the market?

IC Development can take multiple years, will you hit the market window?

August 2020 669

# Market timing Can you hit the window of opportunity?

August 2020 7:50

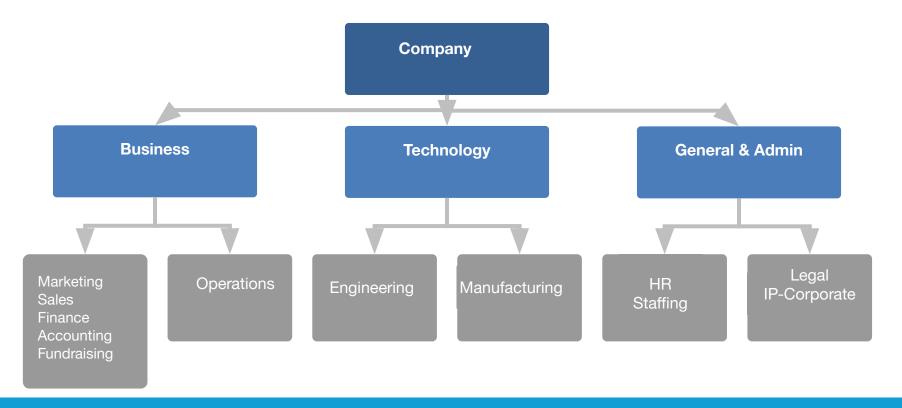

## Building a company takes the right team

SILICON CATALYST it's about what's next.®

Investors want to know you have have the knowledge base for running a company not just building a product

August 2020 8@

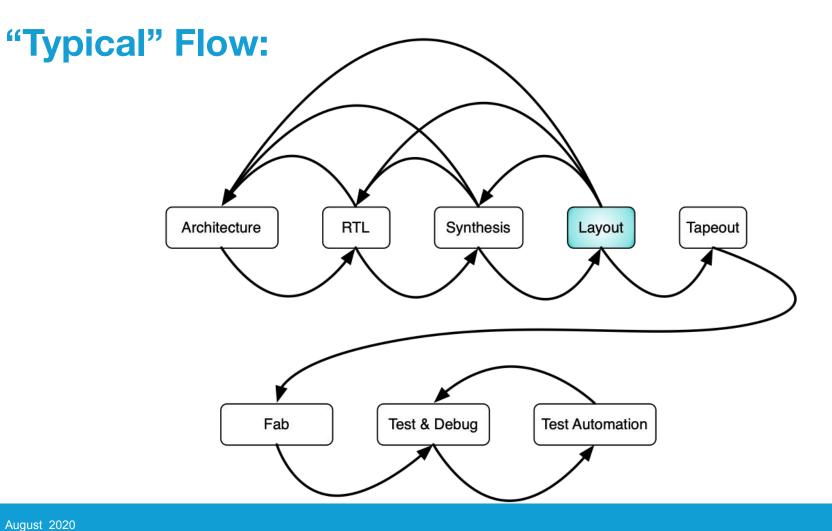

# Path to Product For building an IC

August 2020 9@

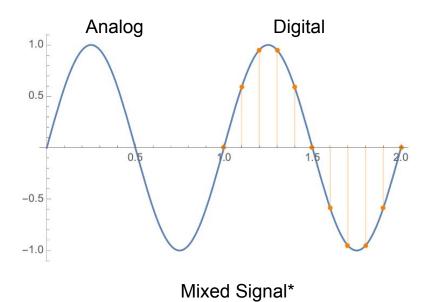

# **Types of ICs**

August 2020 1000

<sup>\* &</sup>lt;a href="https://semiengineering.com/increase-in-analog-problems/">https://semiengineering.com/increase-in-analog-problems/</a>

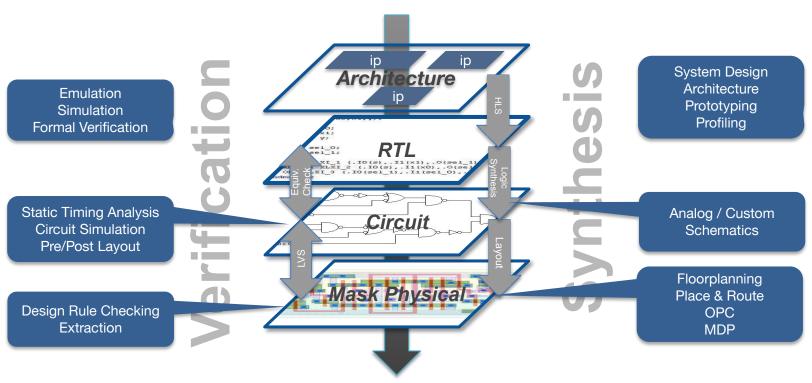

## **IC** Design

August 2020 11@

## **Numerous\* EDA Tools Required**

#### Verification

- Emulation

- System Simulation

- Logic Simulation

- Circuit Simulation

- Static Timing Analysis

- Power Analysis

- Design Rule Check

- Parasitic Extraction

- ...

#### **Synthesis**

- High Level Synthesis

- Floorplanning

- Logic Synthesis

- Technology mapping

- Placement

- Routing

- Optical Proximity Correction

- Mask Data Preparation

- ...

August 2020 12@

<sup>\*</sup> ESDA Lists over 30 *categories* of EDA Tools

it's about what's next.®

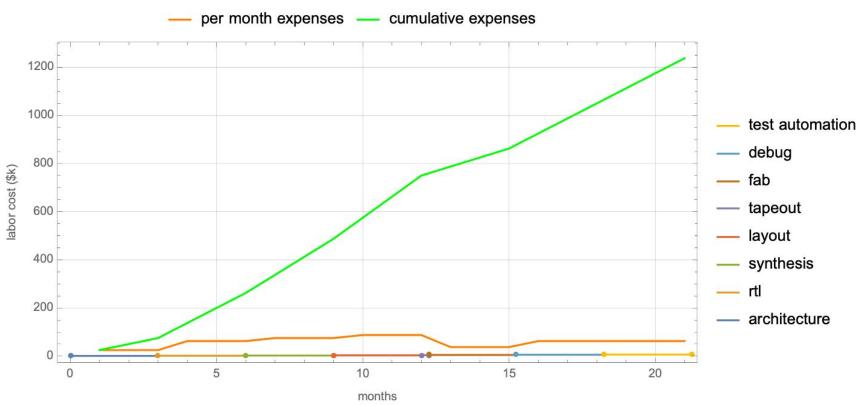

## **Scenario 1: Minimalist**

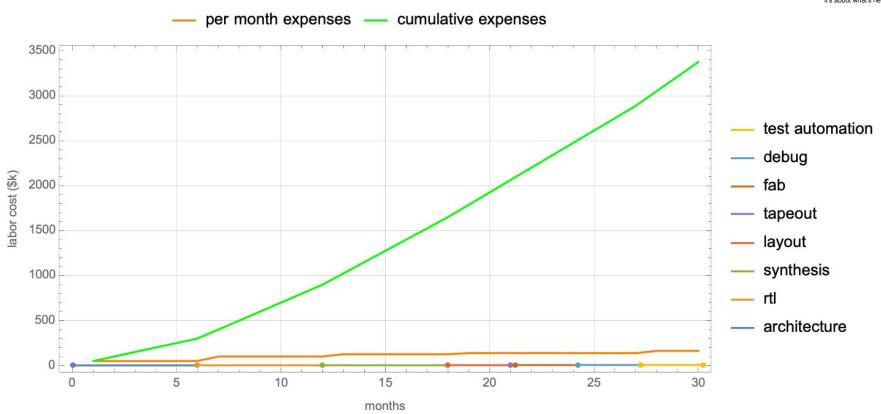

# Scenario 2: Longer Time, Accumulating Staff

August 2020

## **Example 1: Mixed Signal**

## **Example 2: Mostly Analog**

August 2020 17:00

# **Example 3: Digital**

August 2020

## **Maximizing Chance For Success**

August 2020 19:00

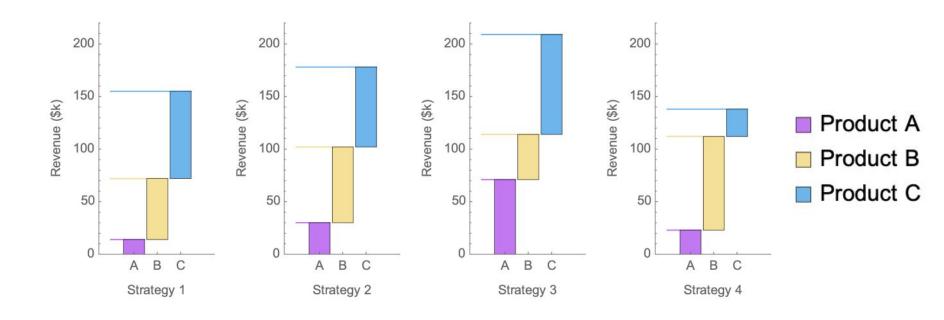

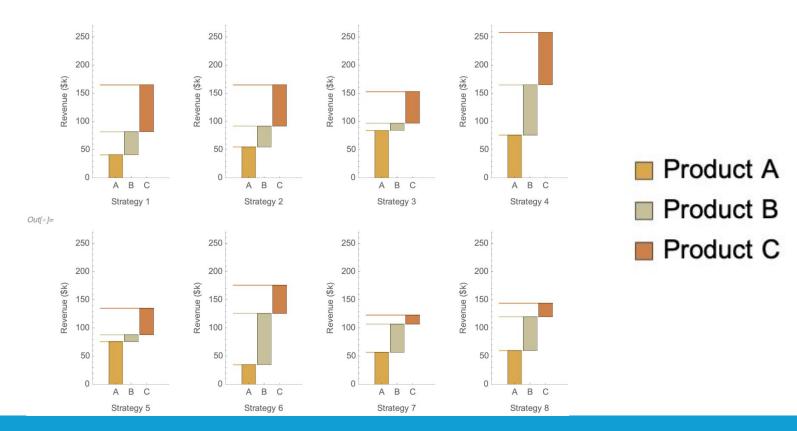

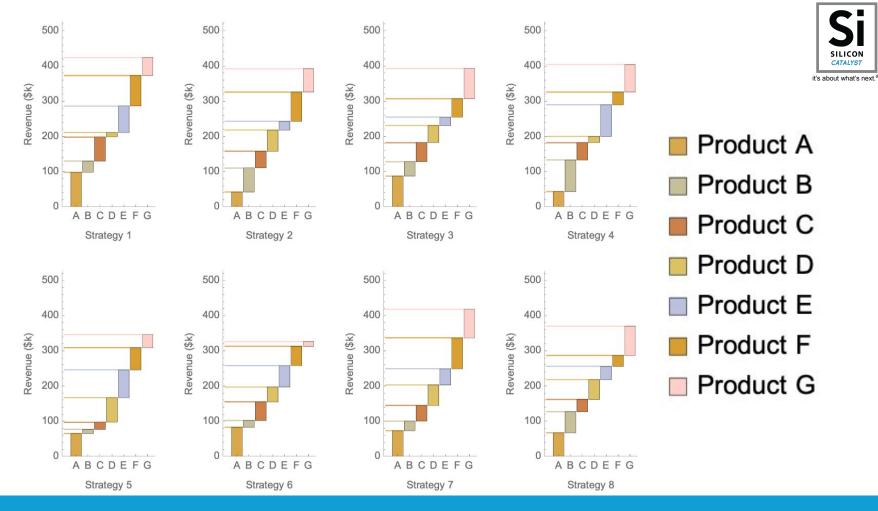

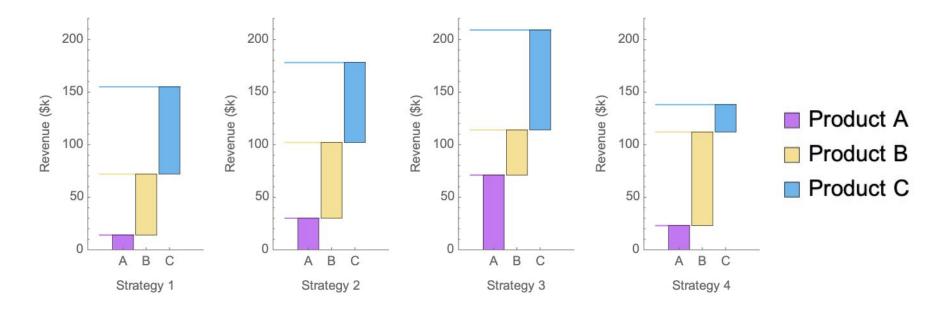

### **Product Mix Example**

August 2020 20@

"It's difficult to raise money for chip startups with Powerpoint or even simulations"

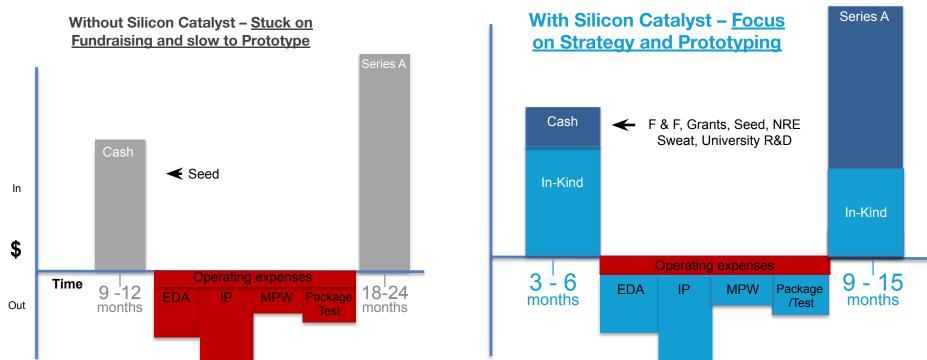

## Reduces the Seed Investment and the Time to Prototype

Silicon Catalyst receives Common Equity in exchange for incubation

August 2020 22@

**Design**

SYNOPSYS° Silicon to Software

**IP**

**Des. Service**

#### **Foundry**

#### Test/backend

#### **Business**

SILICON

CATALYST

it's about what's next.6

**In-Kind Partners**

<sup>1</sup> Low Volume; <sup>2</sup> High Volume Yield Improvement; <sup>3</sup> Israel Only

August 2020

## Our startups launched from Universities

Enabling the next phase of Moore's

Law

through optical connectivity

Hi performance compute for Al

Silicon Photonics on MEMS with the low cost structure of Microelectronics

GHz ultrasonic for Imaging Sensing and IOT

Multi-scale biochemical phenotyping in limited sample volume

Analog In-memory Computing for Al

Embedded SRAM using 1T & 2T cells in standard foundry flow

Ultra-low energy, ultra-low power wireless communications

High-performance AMS designs for consumer medical imaging, 5G and LiDAR

# Join us in driving innovation!

August 2020 25@9

# Architectural Design

Product requirements

Product specification

Data Sheet

3-6 months

\$150K per engineer/yr

EDA Licenses \$100-\$200k/per license

#### Register Transfer Level (RTL)

3-6 months

\$150K per engineer/year

EDA Licenses

\$100-\$200k/per license

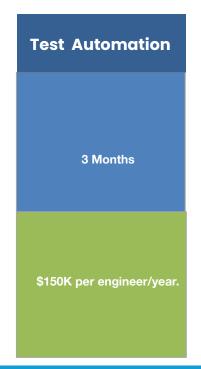

#### Synthesis

3-6 Months

\$150K per engineer/year.

#### Layout

3 Months

\$150K per engineer/year.

August 2020

# **Tape Out** 1 Week \$150K per engineer/yr

August 2020 27:69

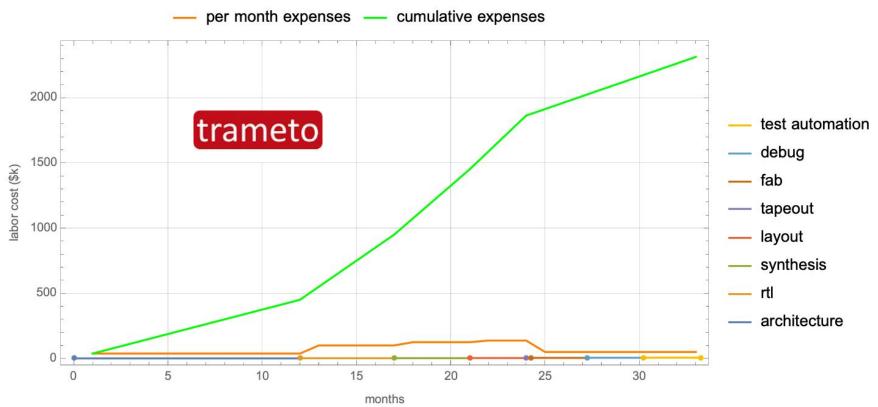

# trameto

10-12 Months

**Architectural**

\$150K per engineer/yr EDA Licenses -\$100-\$200k/per license

# Register Transfer Level (RTL)

5 months

\$150K per engineer/year

EDA Licenses

\$100-\$200k/per license

#### **Synthesis**

4 Months

\$150K per engineer/year.

#### Layout

3 Months

\$150K per engineer/year.

August 2020 28@

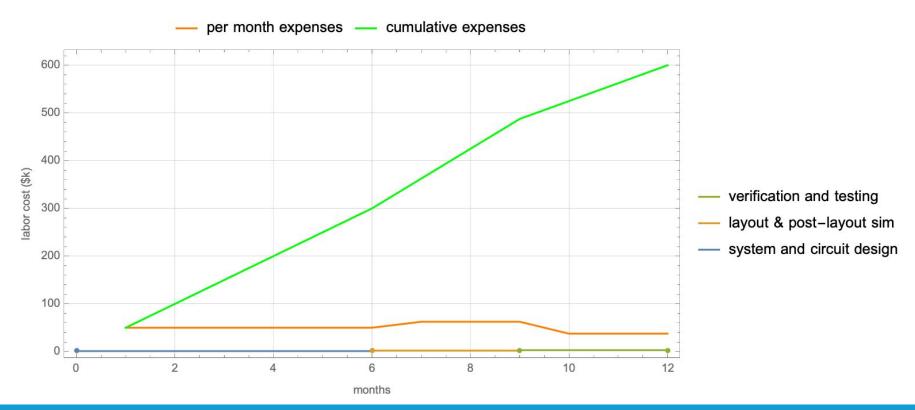

#### Company X- Analog

# System and Circuit Design

Product requirements

Product specification

Data Sheet

4-6 Months

\$150K per engineer/yr EDA Licenses -\$100-\$200k/per license

#### Layout and Post Layout Simulation

3 months

\$150K per engineer/year

EDA Licenses

\$100-\$200k/per license

## Verification and Testing

3 Months

\$150K per engineer/year.

August 2020 29@

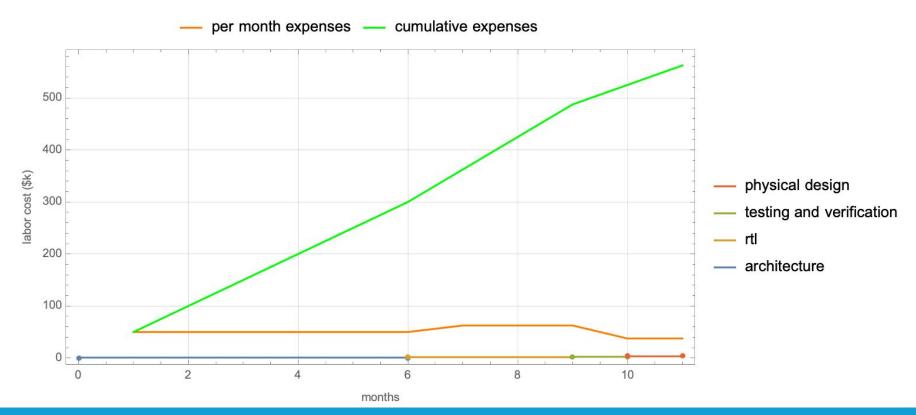

#### Company X- Digital

# Architectural Design

Product requirements

Product specification

Data Sheet

4-6 months

\$

\$150K per engineer/yr

EDA Licenses \$100-\$200k/per license

#### Register Transfer Level (RTL) Synthesis

~3 months

\$150K per engineer/year

EDA Licenses

\$100-\$200k/per license

# Testing and Verification

1 Month

\$150K per engineer/year.

# Physical Design

1 Month

\$150K per engineer/year.

"It's difficult to raise money for chip startups with Powerpoint or even simulations"

Source: Silicon Catalyst, 15 startups surveyed in 2014

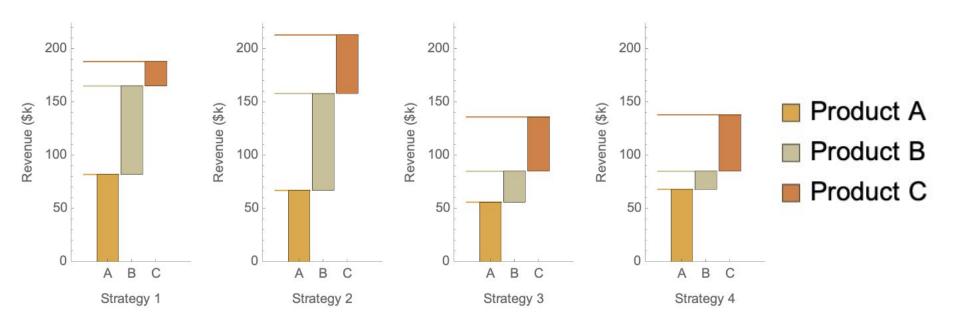

# **Maximizing Chance For Success**

August 2020 32@

"It's difficult to raise money for chip startups with Powerpoint or even simulations"

Time, EDA, Prototypes, Test, \$'s

August 2020

Source: Silicon Catalyst, 15 startups surveyed in 2014

33<sub>08</sub>

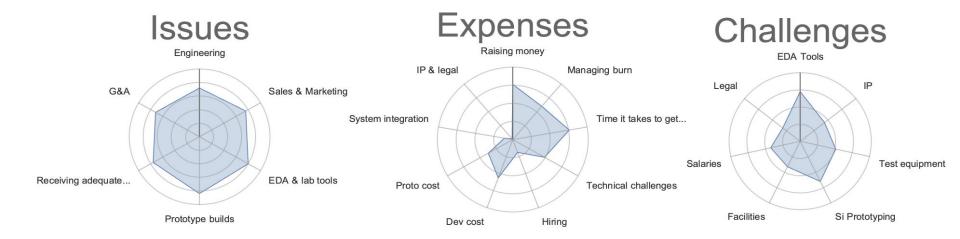

## **Product Mix Example**

August 2020

34<sup>[OBJ]</sup>

August 2020 35:00

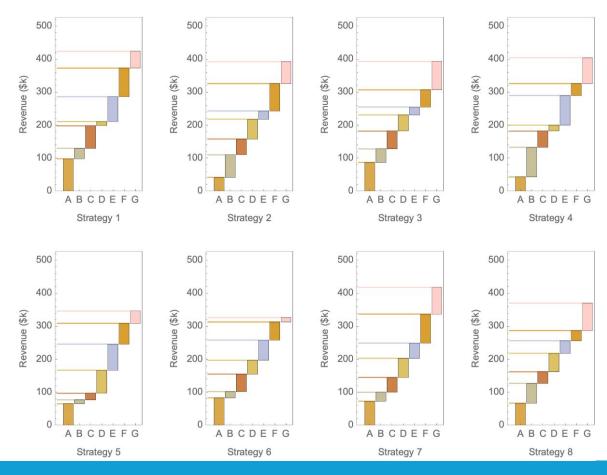

- Product A

- Product B

- Product C

- Product D

- Product E

- Product F

- Product G

August 2020 3669

August 2020 37:66

"It's difficult to raise money for chip startups with Powerpoint or even simulations"

"It's difficult to raise money for chip startups with Powerpoint or even simulations"

Source: Silicon Catalyst, 15 startups surveyed in 2014

August 2020

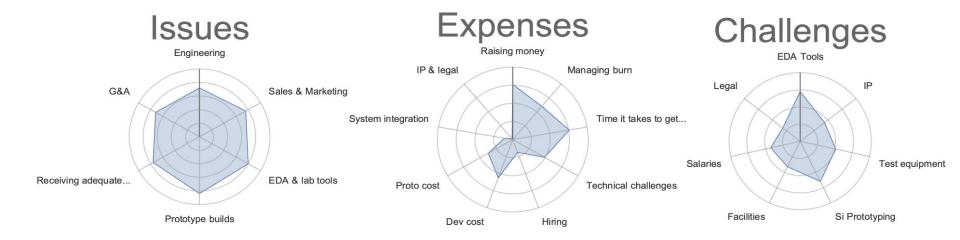

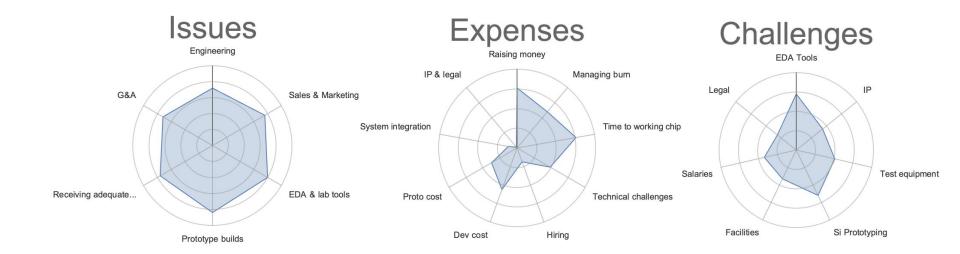

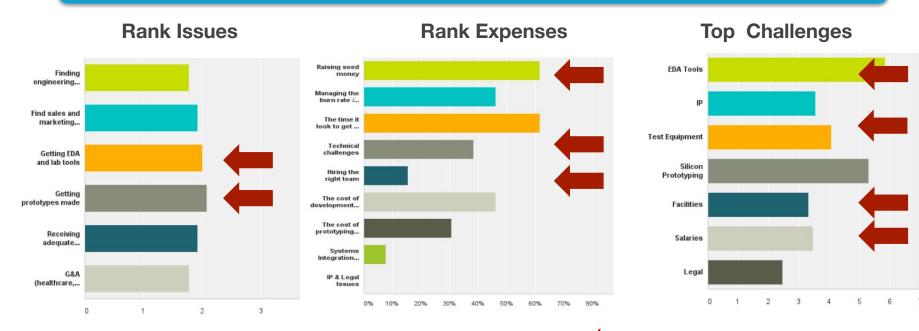

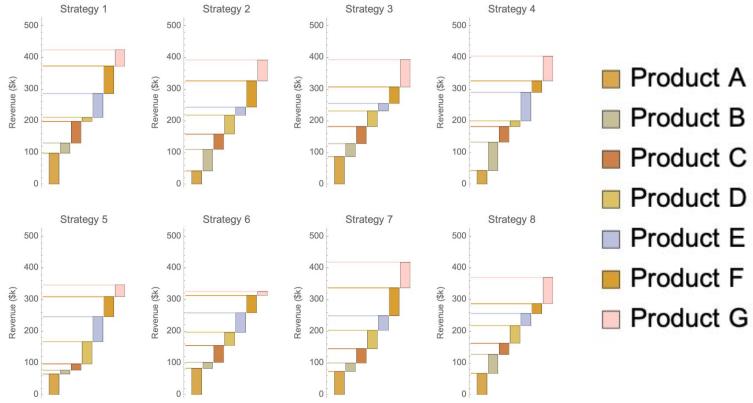

Rank Issues

39<sup>®</sup>

Top Challenges

"It's difficult to raise money for chip startups with Powerpoint or even simulations"

**Rank Issues**

**Rank Expenses**

**Top Challenges**

August 2020 41:00

August 2020 42:00